RESEARCH

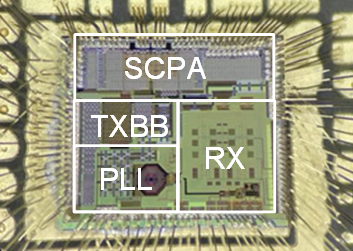

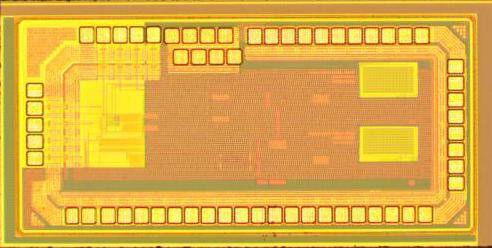

NB-IoT interference suppression transceiver front-end

An NB-IoT interference suppression method based on higher-order statistical characteristics is used to filter out interference signals by detecting whether the input signal contains interference signals and using the difference between these interference signals and NB-IoT signals in the higher-order statistical domain for adaptive filtering, which is characterized by low-power consumption, low-cost, low-noise, and reconfigurable. The application areas are IoT applications, 5G communications, wireless sensors, and narrowband receivers.

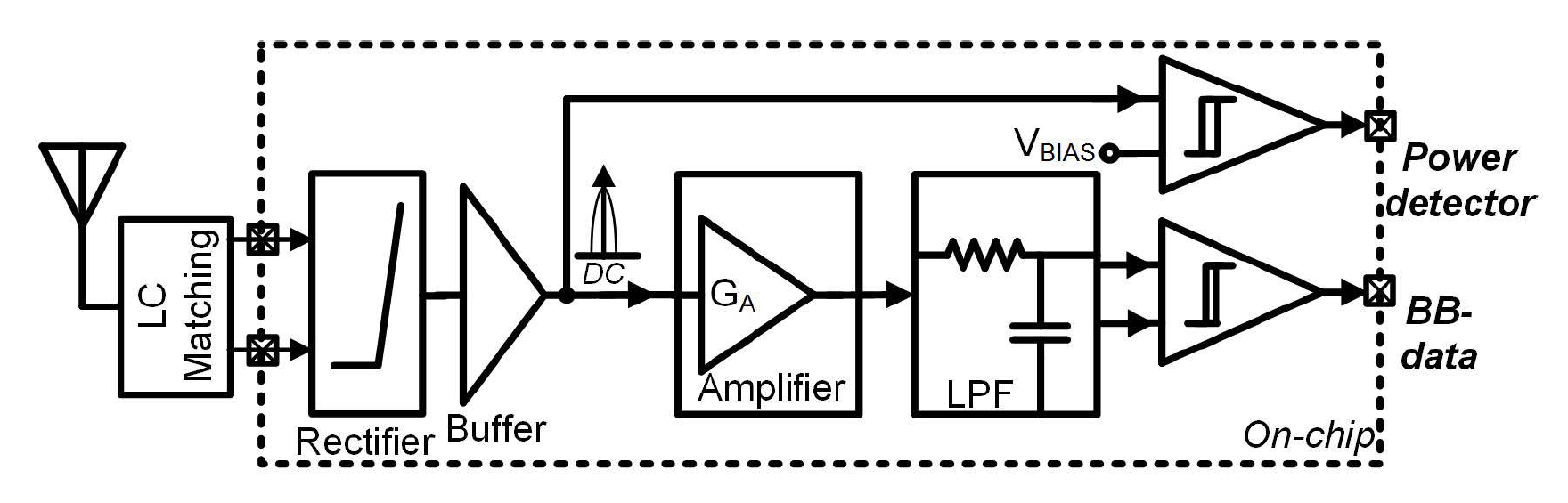

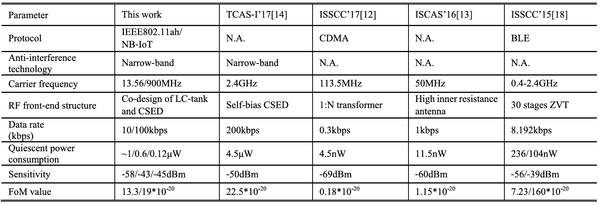

Multi-mode Ultra-low Power Wake-up Receiver

A multi-mode ultra-low power wake-up receiver based on direct envelope detection in HF/UHF band is analyzed and presented, featuring high sensitivity, low power consumption, and HF/UHF.. In order to balance the power consumption and sensitivity, multi-mode with power detection (PD), signal detection (SD), and high sensitivity signal detection (HSSD) are adopted. The application areas include smart sensors, wireless sensor networks, the Internet of Things (IoT), and Wi-Fi applications.

Paper Link:

Analysis and Design of a Multi-Mode Wake-Up Receiver Based on Direct Envelope Detection in Wireless Sensor Networks