Very Small Area Phase-Locked Loop Based on Pulse Shaping and Ring Oscillator

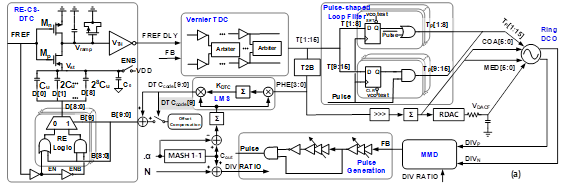

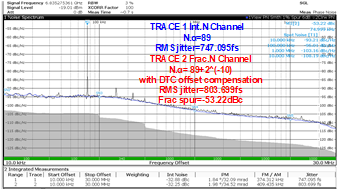

The research team proposed a large loop bandwidth phase-locked loop (PLL) based on pulse shaping. Compared with LC-type oscillators, the phase noise performance of the ring oscillator is poor, although it has an advantage in terms of area. To solve this problem, pulse shaping technique is used to enhance the loop bandwidth of the phase-locked loop, breaking the restriction that the loop bandwidth of a conventional phase-locked loop cannot exceed 10% of the reference clock frequency. In order to eliminate the DSM noise caused by fractional crossover frequency, a range-extended constant-slope digital time converter is used in the design, which effectively increases the range of the digital time converter while the area of the capacitor array remains unchanged. At the same time, the linearity of the digital time converter is further improved by combining the effective channel length modulation effect and the variable load capacitance effect. The phase-locked loop is implemented based on a 28nm CMOS process and exhibits a fractional 10kHz to 30MHz integration noise of 803.7fs, integer boundary spurious of -53dBc, a core area of 0.025mm², a FoMjitter-N-Area of -269.9, and an energy efficiency of 0.83mW/GHz at a frequency of 6.8GHz.

The related results were published in the 2024 ESSERC conference, with Hao Yuan Gao, a PhD student at the School of Microelectronics, Fudan University, as the first author.

Paper Link: