研究领域

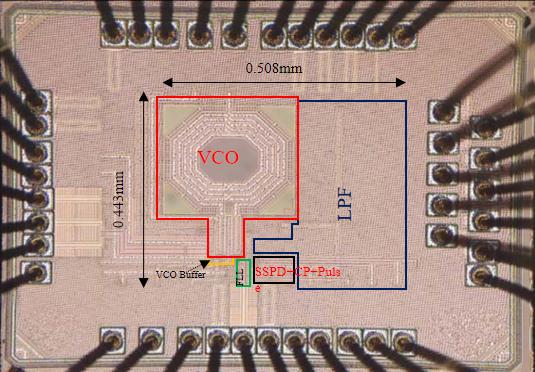

低功耗低杂散2.4GHz亚采样锁相环

一种模拟的低功率子采样锁相环(PLL),它处理了子采样操作中由VCO负载调制引起的参考支路。对二元频移键控(BFSK)效应进行了完整的分析,具有自适应、低噪声、低功耗的特色。其应用领域为5G或卫星通信、高速数据转换器时钟等。

相关论文:

Analysis and Design of a Sub-Sampling PLL of Low Phase Noise and Low Reference Spur *该论文为封面文章

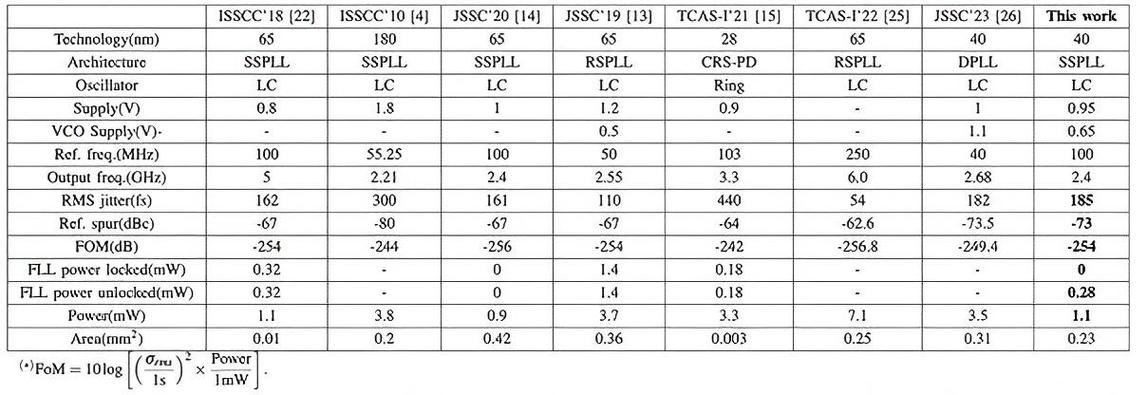

应用于物联网的全数字频率综合器

一种用于窄带物联网应用的低功耗分数-n全数字PLL(ADPLL)。多步锁定控制和振荡器调谐字粗预测算法有助于加速锁定过程到20µs以下。数字-时间转换器(DTC)与相位预测算法一起使用能够尽量减少低功耗的时间-数字转换器的检测范围。具有高性能、低功耗、面积小、可重构的特点。应用领域为窄带物联网应用、5G通信。

相关论文:

A Low Power All-Digital PLL With −40dBc In-Band Fractional Spur Suppression for NB-IoT Applications

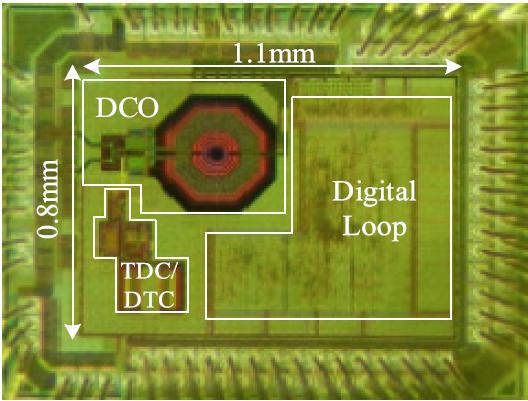

8-14GHz宽带整数分频时钟芯片

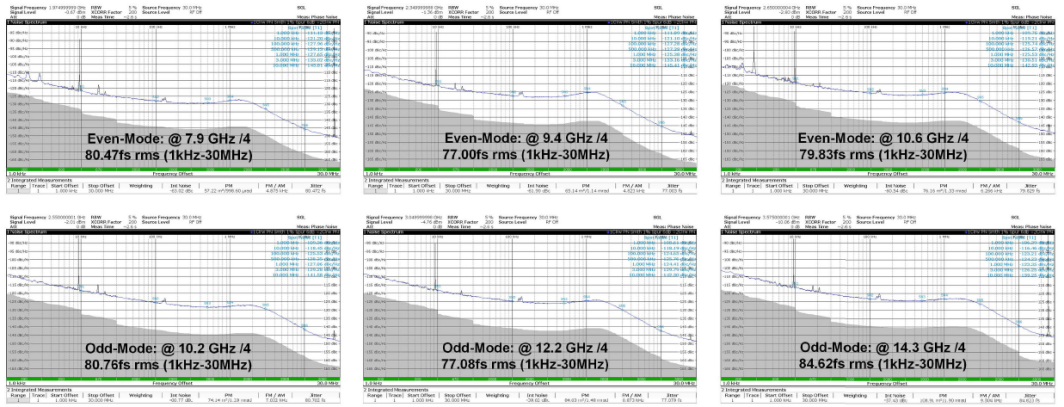

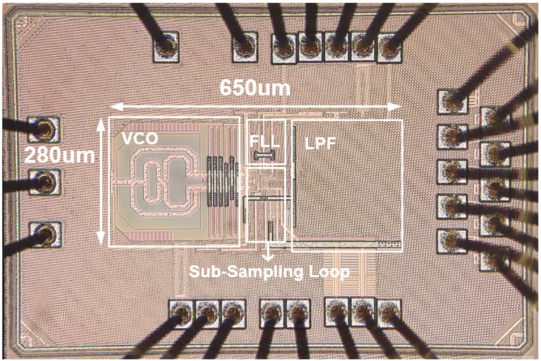

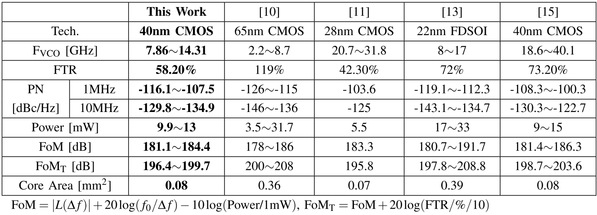

一种利用双模电压控制振荡器(VCO)的宽带、低抖动频率合成器。实现的双模VCO抑制了工作频率范围内的相位噪声(PN)差异,这进一步使子采样锁相环(SSPLL)在宽频率范围内实现接近最小的抖动,而没有环路增益自适应。

相关论文:

A 7.9-14.3GHz -243.3dB FoMT Sub-Sampling PLL with Transformer-Based Dual-Mode VCO in 40nm CMOS

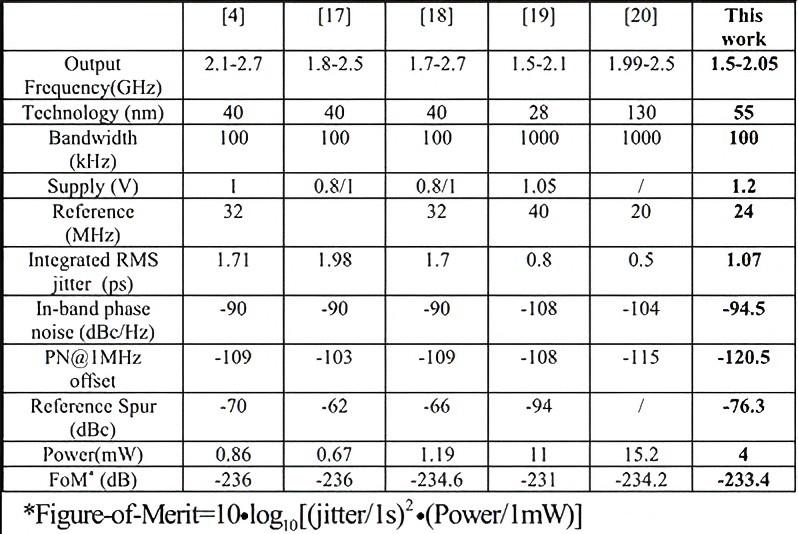

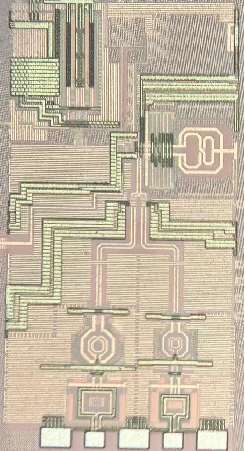

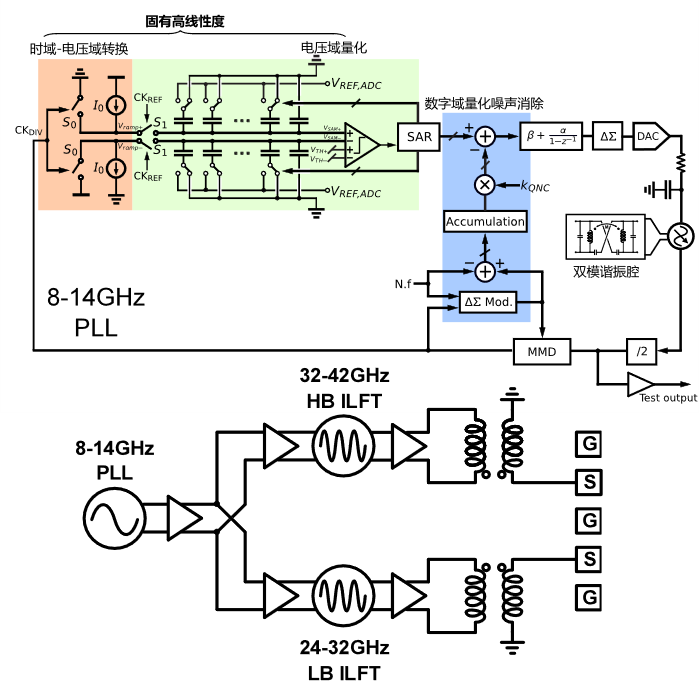

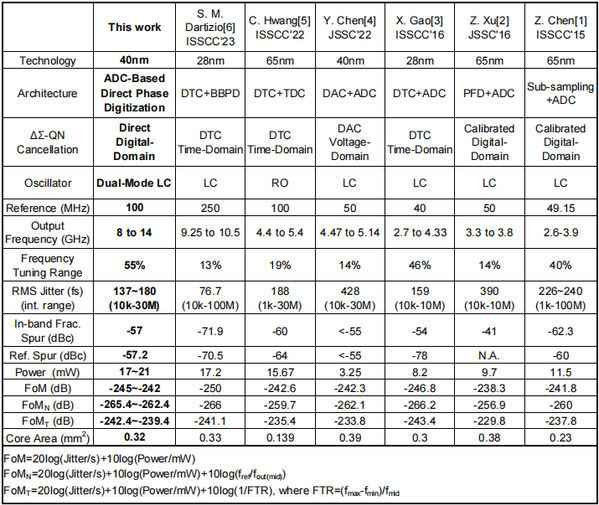

8-14GHz/23-42GHz宽带小数分频时钟芯片

具有高频率分辨率和低相位噪声的宽频率覆盖锁相环(PLL)是高速通信系统的关键组成部分之一。无DTC/DAC和线性校准的PLL具有先进优点,所提出的内在高线性的相位数字化方案在更高级的流程节点中得到优化。

相关论文:

An 8-14GHz 180fs-rms DTC-Less Fractional ADPLL with ADC-Based Direct Phase Digitization in 40nm CMOS