An All-Digital Spread-Spectrum Clock Generator with Feedforward Gain Calibration

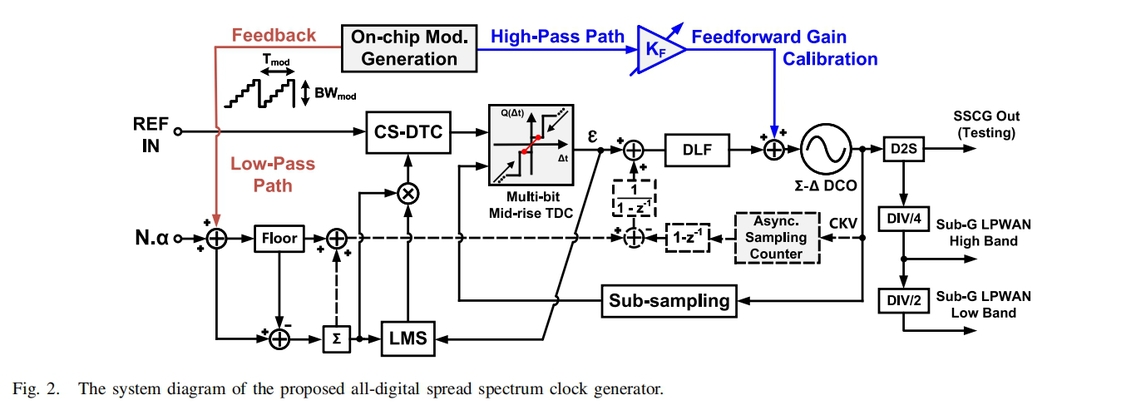

The research team presents an all-digital spread-spectrum clock generator (AD-SSCG) for chirp spread spectrum applications in low-power wide-area networks (LPWAN). To address periodic frequency hopping in chirp modulation, we propose a feedforward gain calibration technique that effectively eliminates two-point modulation (TPM) loop-gain mismatch and phase error, ensuring precise frequency tracking. By integrating a constant-slope digital-to-time converter (CS-DTC) with a multi-bit mid-rise time-to-digital converter (TDC), the embedded digital loop achieves linear sawtooth chirp modulation while maintaining excellent phase noise (PN) performance. Fabricated in 40nm CMOS technology, the prototype chip demonstrates 508fsrms random jitter and -111.6dBc/Hz@1MHz phase noise at 2.45mW power consumption, with 39.1dB EMI reduction (4MHz modulation bandwidth + 2000ppm modulation depth).

This work was published in IEEE Transactions on Circuits and Systems II (TCAS-II) in 2025, with Yiyun Mao as first author. He is currently pursuing the Ph.D. degree in integrated circuit science and engineering with Fudan University, Shanghai.