RFiCAE课题组2025年度科研成果(六):0.06mm2基于折叠环形变压器的14.7-20.2 GHz四核压控振荡器

发布时间:2025-05-19

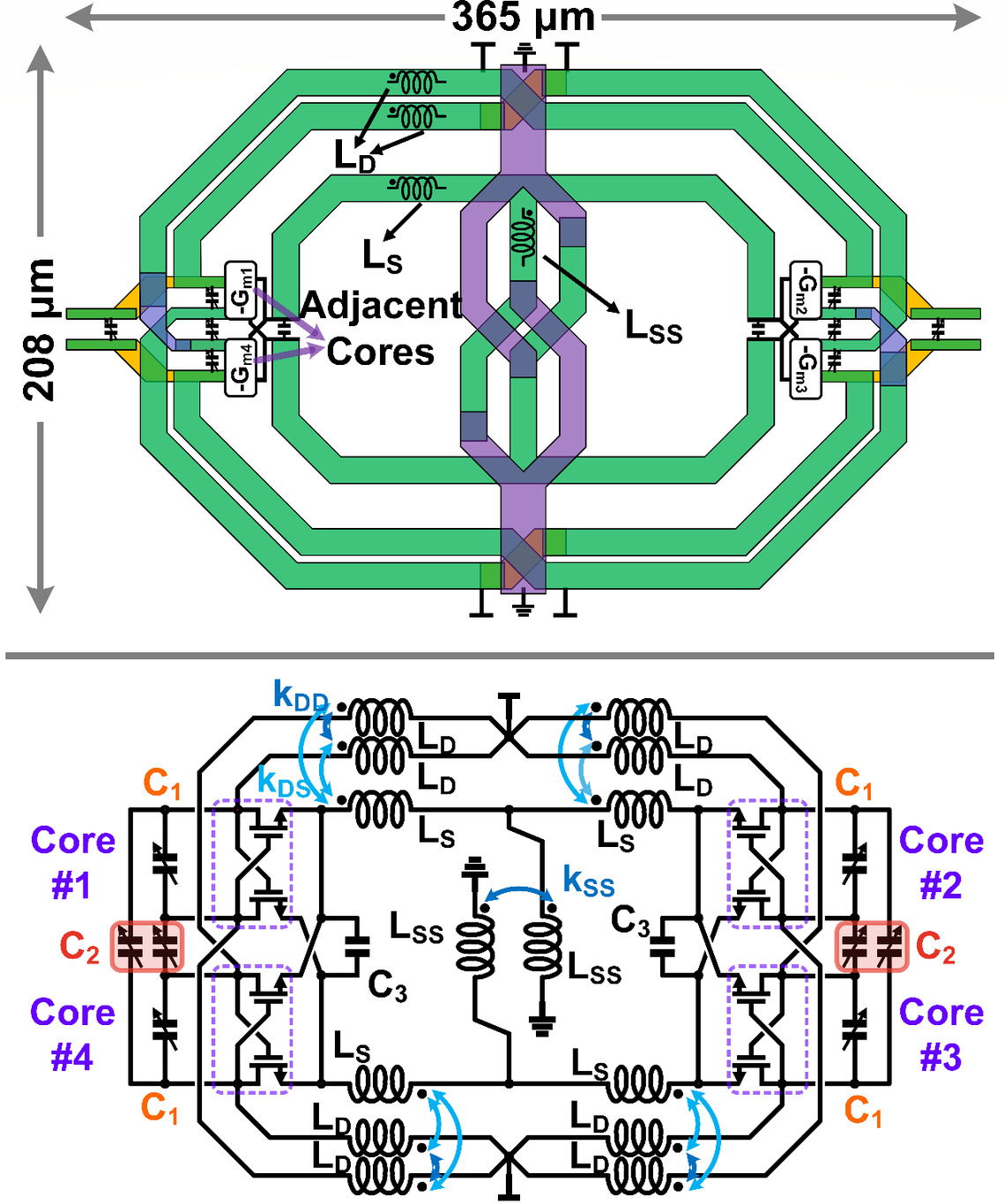

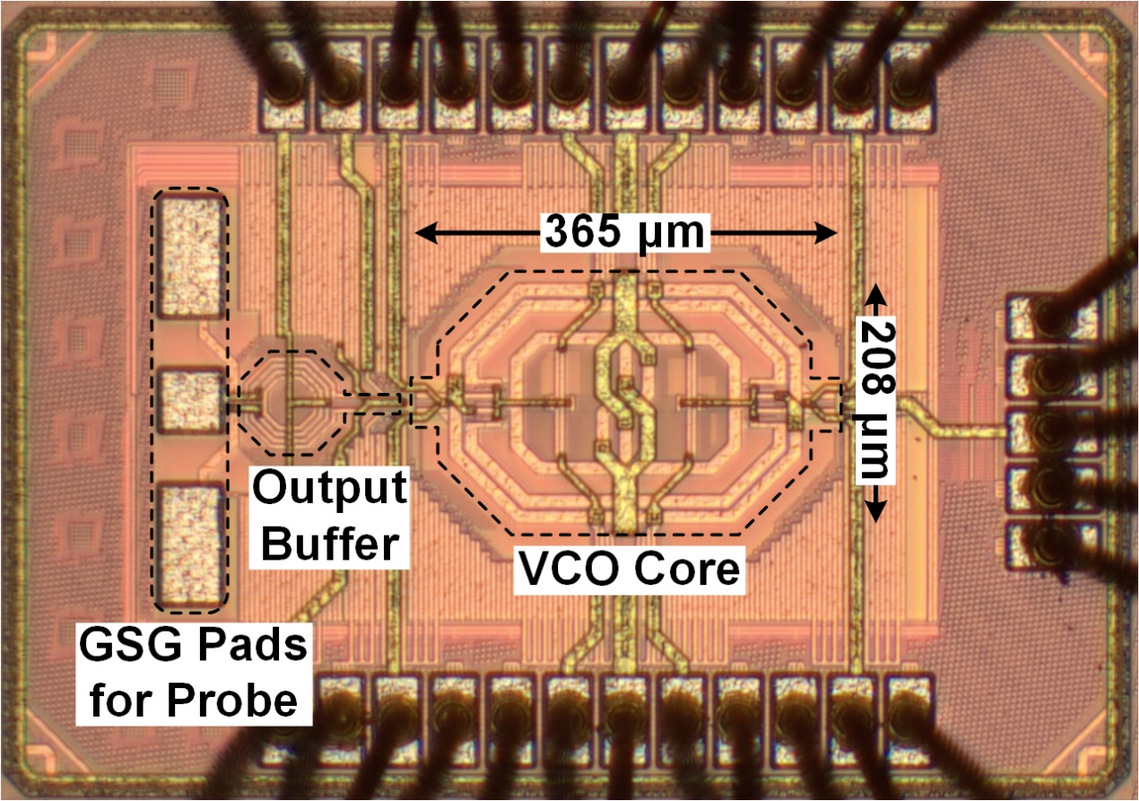

研究团队提出了一种基于折叠环形变压器的小面积,高性能,强同步四核压控振荡器(Quad-Core VCO)。针对传统四核谐波振荡器面积大,频率失配后相噪惩罚大,同步网络高寄生等难题,提出了一种折叠环形变压器的无源设计。此设计不仅极大地压缩了四核振荡器所占用的片上面积,还存在多条感性同步通路且支持引入核间电容作为容性同步通路,从而形成一种低寄生的多通道磁场-电场强同步网络,大大地降低了核间频率失配带来的相噪惩罚。此外,无源电感形成的电流通路支持差模,共模两种模式下的品质因数增强,支持高质量的共模二阶谐波整形,实现1/f3噪声的抑制。该四核振荡器芯片采用28nm CMOS工艺实现,在5mW的功耗和0.06mm²的面积下覆盖了14.7至20.2GHz的频率范围,10MHz频偏下FoMA和FoMT达到了203.4和201.1dBc/Hz,且实现了350至700kHz的1/f3噪声转角频率。

相关成果以“A 0.06mm2 14.7-to-20.2GHz Quad-Core VCO Enabled by the Folded Circular Transformer Achieving 201.1dBc/Hz FoMT and 203.4dBc/Hz FoMA”发表于国际集成电路顶级会议2025 VLSI,复旦大学微电子学院本科生欧天政为第一作者,许灏青年研究员和闫娜教授为通讯作者。