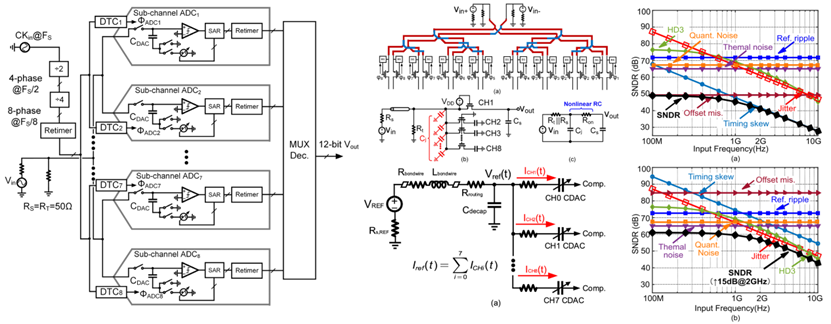

Systematic Design of a 3.5 GS/s 11-bit Time-Interleaved SAR ADC in 28 nm CMOS Achieving 54 dB SNDR at Nyquist Frequency

发布时间:2025-05-19

This paper presents a design-oriented analysis for the time-interleaved SAR ADC that quantifies different sources of imperfections to provide a unified design framework. The impact of nonlinear junction capacitors on distortion, design optimization of the multi-phase clock generation circuits and the impact of reference ripple in the context of time-interleaving are analysed. The time-interleaved SAR ADC is implemented in 28 nm CMOS following the presented design optimization. The 3.5 GS/s 11-bit ADC achieves 54 dB dSNDR at 1.74 GHz input frequency with 51mW core power.