RFiCAE课题组2025年度科研成果(一):基于双反馈环路环形振荡器的 8~28 GHz 八相位时钟发生器

发布时间:2025-03-04

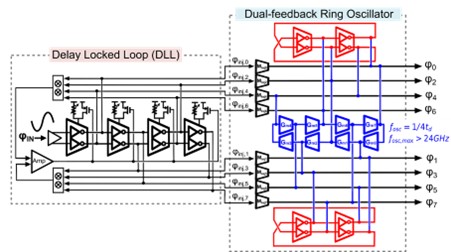

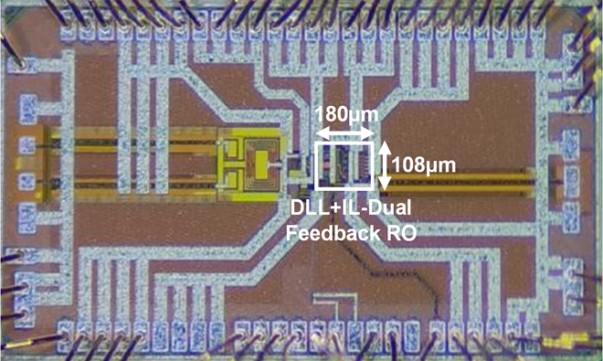

面向下一代超高速有线通信接口电路中高数据传输速率与低时钟抖动的需求,研究团队提出一种超宽频带覆盖、低相位噪声、高相位精度的八相位时钟产生电路。所提出的双反馈环路环形振荡器,通过解耦频率产生环路和相位同步环路,显著提升了给定工艺节点下环形振荡器的最高振荡频率和工作频带覆盖范围。此外,利用宽带延时锁相环产生的低时钟抖动八相位信号注入锁定环形振荡器,在不恶化相位噪声的基础上,提高了输出相位精度。该工作在8~28GHz八相位时钟信号输出频率下,实现了小于38fs的时钟抖动和小于3度的相位误差,在所有国际上已报道的多相位时钟工作中,该工作实现了最宽工作频带和最小时钟抖动。

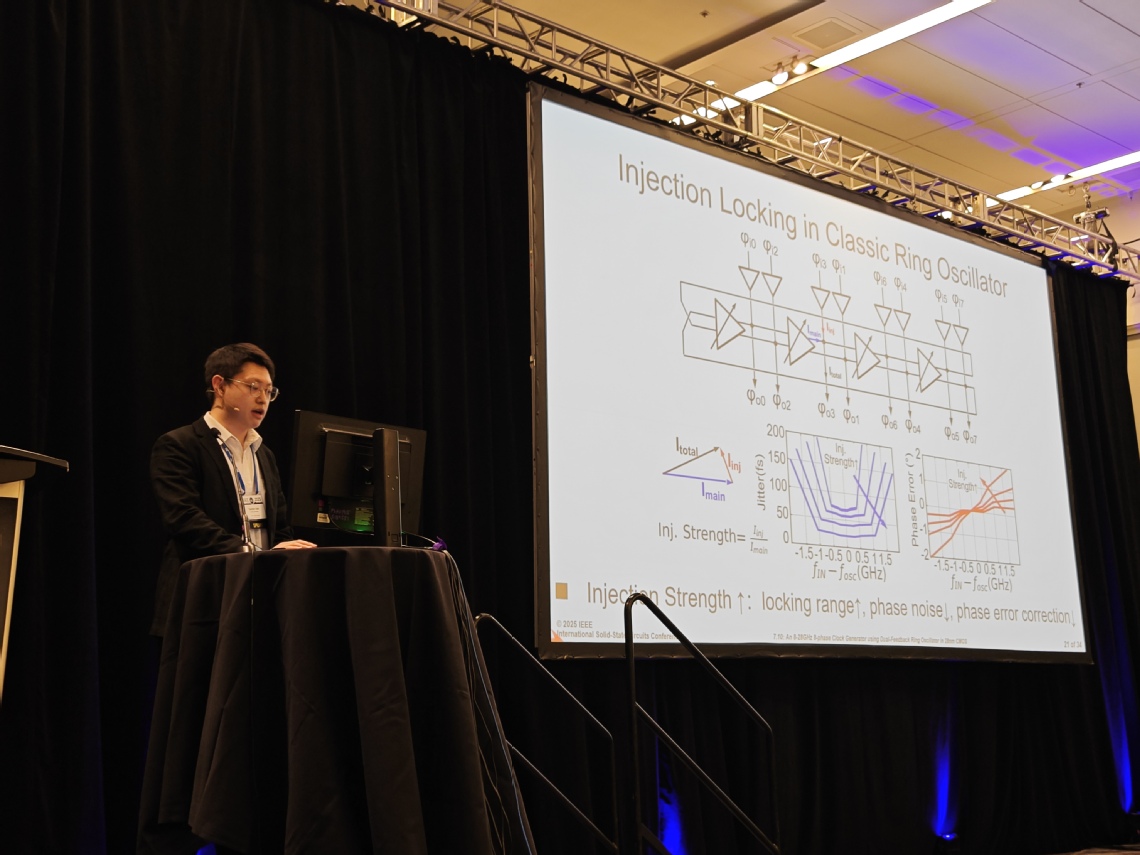

该工作以“An 8-to-28GHz 8-Phase Clock Generator Using Dual-Feedback Ring Oscillator in 28nm CMOS”为题,发表于2025年ISSCC的高速有线通信(High Speed Wireline)分会场。该论文第一作者为复旦大学博士研究生田野辰,通讯作者为复旦大学闫娜和许灏教授,文章由第一作者田野辰博士研究生进行演讲汇报。