RFiCAE课题组2024年度科研成果(五):基于脉冲整形和环形振荡器的极小面积锁相环

模拟芯片是我国集成电路产品的重要基石,是国家安全保障和高质量发展不可或缺的重要基础支撑。在技术进步和市场需求的双重推动下,模拟芯片在多个领域展现出巨大的发展潜力和应用价值。同时,面对国内外的挑战,加强自主创新和推动国产化进程也是未来模拟芯片创新体系发展的重要方向。复旦大学RFiCAE课题组在闫娜教授、许灏青年研究员的指导下,在低功耗无线通信收发芯片、宽带射频收发芯片、高性能锁相环、高速模数/数模转换器、高能效混合信号芯片设计等方面取得了一系列的研究成果,发表于IEEE JSSC、IEEE TCAS-I、IEEE TMTT、IEEE ISSCC/RFIC/CICC/ESSERC等国际著名期刊会议上。

(五)基于脉冲整形和环形振荡器的极小面积锁相环

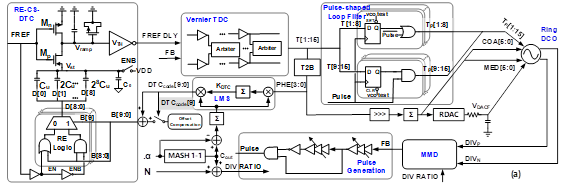

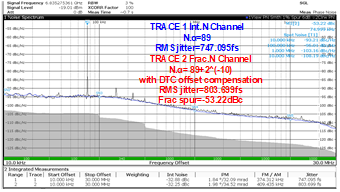

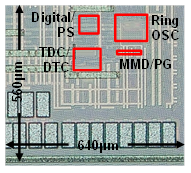

研究团队提出了一种基于脉冲整形的大环路带宽锁相环(PLL)。与LC型振荡器相比,环形振荡器虽然在面积上具有优势,但其相位噪声表现较差。为解决这一问题,采用脉冲整形技术提升了锁相环的环路带宽,突破了传统锁相环环路带宽不能超过参考时钟频率10%的限制。为了消除小数分频带来的DSM噪声,设计中采用了量程扩展型恒定斜率数字时间转换器,在电容阵列面积不变的情况下,有效增加了数字时间转换器的量程。同时,结合有效沟道长度调制效应和可变负载电容效应,进一步提升了数字时间转换器的线性度。该锁相环基于28nm CMOS工艺实现,在6.8GHz频率下,展现出小数10kHz至30MHz的积分噪声为803.7fs,整数边界杂散为-53dBc,核心面积为0.025mm²,FoMjitter-N-Area为-269.9,能效为0.83mW/GHz。

相关成果发表在2024 ESSERC会议上,复旦大学微电子学院博士生高皓原为第一作者。

论文信息: