RFiCAE课题组2025年度科研成果(五):采用前馈路径增益校准的全数字扩频时钟发生芯片

发布时间:2025-05-19

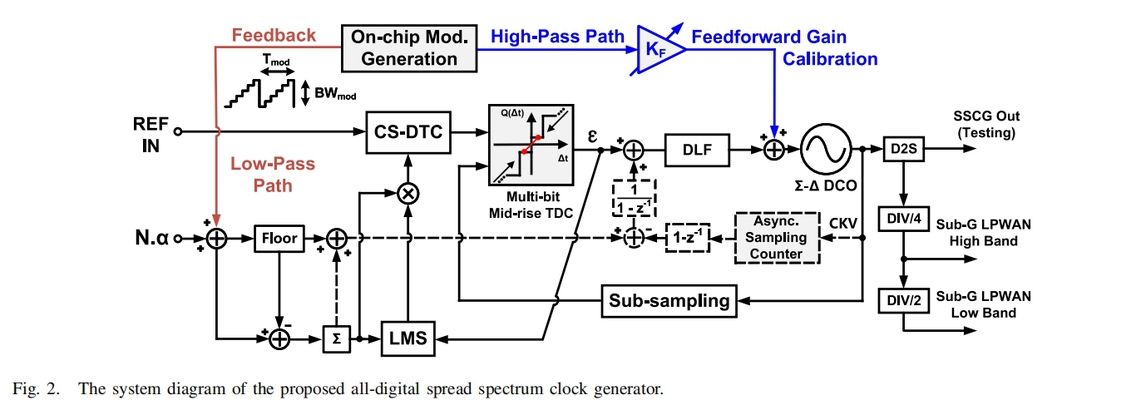

研究团队提出了一种面向低功耗广域网(LPWAN)线性调频扩频应用的全数字扩频时钟发生器(AD-SSCG)。针对线性调频调制中的周期性跳频特性,提出了一种在前馈路径中采用增益校准技术,有效避免了两点调制(TPM)环路增益失配与相位误差,确保了精准的频率跟踪。通过结合恒定斜率数字时间转换器(CS-DTC)和多比特中升型时间数字转换器(TDC),嵌入式数字环路在保持优良相位噪声(PN)性能的同时,实现了线性锯齿波调频调制。该芯片采用40nm CMOS工艺实现,在2.45mW的功耗下实现了508fsrms的随机抖动,相位噪声为-111.6dBc/Hz@1MHz,电磁干扰抑制可达39.1dB(4MHz调制带宽+2000ppm调制深度)。

相关成果发表于国际电路与系统顶级期刊IEEE TCAS-II 2025(中科院二区),复旦大学微电子学院博士生毛毅赟为第一作者。