RFiCAE课题组2025年度科研成果(三):3.5GS/s 11位分辨率54dB SNDR高速时间交织SAR ADC系统设计方法

发布时间:2025-05-19

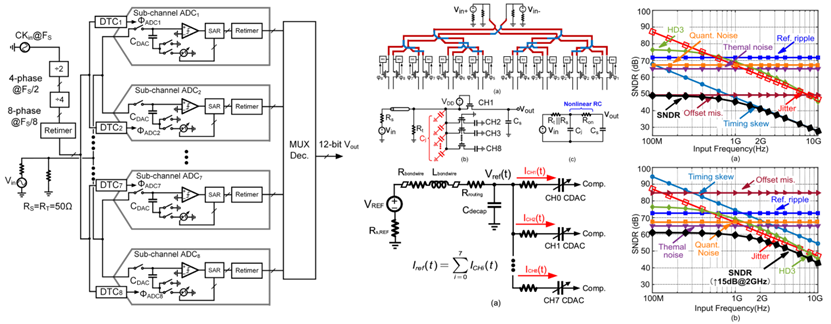

研究团队提出了面向高速时间交织SAR ADC的定量分析和设计框架。对多通道采样非线性进行了定量分析评估;针对时间交织相位失配,阐述了多相时钟生成电路的设计优化方法,使功耗与抖动之间的权衡关系变得清晰;同时对多通道间参考电压的串扰和抖动进行了建模和分析,得到退耦电容和噪底以及失真的定量关系。该模数转换器芯片采用28nm CMOS工艺实现,以51mW的功耗实现3.5GS/s的采样率,在奈奎斯特输入频率下信号噪声失真比达到54dB。

相关成果发表于国际集成电路设计领域顶级期刊IEEE TCAS-I 2025,复旦大学微电子学院博士生柳帅为第一作者。